Teng Wang defends his thesis on self-adjusting and linearization techniques based on digital predistortion for communications in UAVs.

Dec 21, 2020

Teng Wang defended his thesis titled "A Fasto Engineering Approach High Efficiency Power Amplifier Linearization for Avionics Applications" on December 17 at EETAC, directed by Pere L. Gilabert (TSC-UPC). The thesis provides some guidelines for the design of linearizers based on digital predistortion (DPD) from several perspectives: y) improve the performance of open-loop DPD, ii) provide robustness and reduce the computational complexity of the parameter identification subsystem and, iii ) incorporation of machine learning techniques to favor the auto-tuning of power amplifiers and DPD linearizers with various degrees of freedom to be able to maximize energy efficiency while meeting linearity specifications.

One of the essential parts of unmanned aerial vehicles (UAV) is avionics, radio control feels one of the first systems present to UAVs. To transfer user data (such as images, video, etc.) in real time from the drone to the ground station, large transmission rates are required. The PA is a key element of the transmitter chain to be able to guarantee the transmission of data over long distances from the ground station. The higher the output power, the more coverage or, alternatively, with the same coverage, the better the signal-to-noise ratio (SNR), which allows the use of higher-order modulation schemes and, therefore, achieve higher transmission speeds. In the context of wireless communications between UAVs, the power consumption, the size and the weight of the payload are of vital importance.

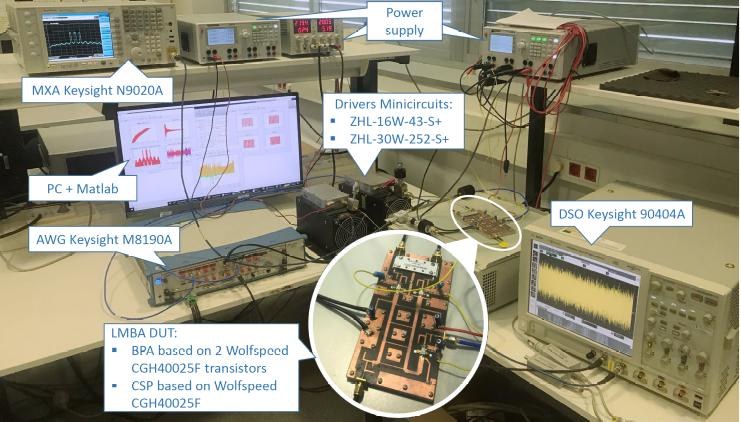

Therefore, the design of the AP has to take into account the trade-off between bandwidth, power output, linearity, and energy efficiency (very critical in battery-powered devices). The PA can be designed to maximize its energy efficiency or its linearity, but not both. Therefore, to meet this compromise, high-efficiency amplifier topologies are used and the linearitzator is left in charge of guaranteeing the necessary levels of linearity. Among linearizers, DPD linearization is the preferred solution for both academia and industry, due to its high flexibility and performance. To save both computational resources and power consumption, the implementation of an open loop DPD is a very attractive solution for UAV applications. This thesis contributes to the linearization of PA, especially to offline training of open-loop DPD linearizers, presenting two different methods to reduce computational cost and increase the reliability of open-loop DPDs. The first method focuses on the analysis of the input signal statistics, proposing mesh selection methods (Mes) to select the most significant samples for a computationally efficient estimation of the DPD parameters. The proposed IQ Month memory method can be combined with reduction techniques of the DPD model and thus be able to achieve a reduction in computational complexity in the identification subsystem by a factor of 65, compared to the use of the classical QR algorithm -LS and selection of consecutive training samples. The second method involves the use of machine learning techniques by the DPD design when considering a large number of degrees of freedom (parameters) to tune. On the one hand, the adaLIPO global optimization algorithm is used to find the best parameter setting of a polynomial model with generalized memory for DPD. On the other hand, a strategy is proposed for the global optimization of a set of key parameters for the design at the circuit and system level, which combined with DPD linearization and crest factor reduction techniques, can maximize input efficiency. dual bandwidth, while meeting linearity specifications. The advantages of these proposed techniques have been validated through experimental tests and the results obtained are analyzed and discussed throughout this thesis.Photograph of the seven-up validation to test the auto-tuning and linearization algorithms of a highly efficient broadband amplifier based on a balanced architecture with load modulation.

Share: